## Highlights

Superconducting and correlated low dimensional materials and devices for quantum electronics and spintronic - 2018

## Hysteresis in the transfer characteristics of MoS<sub>2</sub> transistors

Antonio Di Bartolomeo<sup>1,2</sup>, Luca Genovese<sup>1</sup>, Filippo Giubileo<sup>2</sup>, Laura lemmo<sup>1</sup>, Giuseppe Luongo<sup>1,2</sup>, Tobias Foller<sup>3</sup> and Marika Schleberger<sup>3</sup>

<sup>1</sup> Physics Department, University of Salerno, 84084 Fisciano, Salerno, Italy

<sup>2</sup> CNR-SPIN, c/o Università di Salerno- Via Giovanni Paolo II, 132 - 84084 - Fisciano (SA), Italy

<sup>3</sup> Fakultät für Physik and CENIDE, Universität Duisburg-Essen, Lotharstrasse 1, D-47057, Duisburg, Germany

## 2D MATERIALS 5 (2018) 015014

Molybdenum disulfide (MoS<sub>2</sub>) has recently become one of the most popular semiconductors from the family of the transition metal dichalcogenides. The MoS<sub>2</sub> bandgap can be controlled by the number of layers: Bulk MoS<sub>2</sub> has an indirect bandgap of 1.2 eV while monolayer MoS<sub>2</sub> has a direct bandgap of 1.8 eV. The large bandgap, combined with mechanical flexibility, makes MoS<sub>2</sub> suitable as channel in field effect transistors (FETs) for logic applications.

We investigate the origin of the hysteresis observed in the transfer characteristics of back-gated field effect transistors with an exfoliated MoS<sub>2</sub> channel. We find that the hysteresis is strongly enhanced by increasing either gate voltage, pressure, temperature or light intensity. Our measurements reveal a step-like behavior of the hysteresis around room temperature, which we explain as water-facilitated charge trapping at the MoS<sub>2</sub>/SiO<sub>2</sub> interface. We conclude that intrinsic defects in MoS<sub>2</sub>, such as S vacancies, which result in effective positive charge trapping, play an important role, besides H<sub>2</sub>O and O<sub>2</sub> adsorbates on the unpassivated device surface. We show that the bistability associated to the hysteresis can be exploited in memory devices.

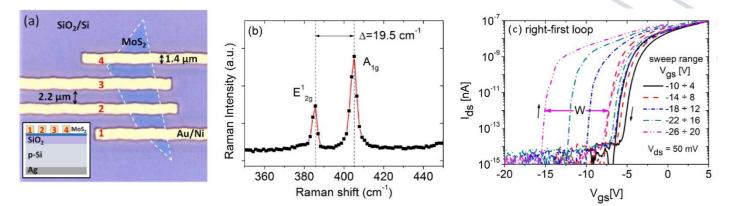

**Figure 1.** (a) Optical image of a monolayer  $MoS_2$  flake (highlighted by dashed white lines) contacted with Ni/Au leads; the inset shows the schematic cross-section of the back-gated FET. (b) Raman spectrum of the  $MoS_2$  flake. (c) Transfer characteristics of the  $MoS_2$  transistor for the back-gate voltage, Vgs , in loops of different amplitudes but with fixed steps (Vgs = 0.1 V).