## Highlights

Other Materials -2017

## Hybrid graphene/silicon Schottky photodiode with intrinsic gating effect

A. Di Bartolomeo<sup>1,2</sup>, G. Luongo<sup>1</sup>, F. Giubileo<sup>2</sup>, N. Funicello<sup>1</sup>, G. Niu<sup>3</sup>, T. Schroeder<sup>4,5</sup>, M. Lisker<sup>4</sup> and G. Lupina<sup>4</sup>

<sup>1</sup>Physics Department 'E. R. Caianiaello', University of Salerno, via Giovanni Paolo II, Fisciano 84084, Italy <sup>2</sup>CNR-SPIN Salerno, via Giovanni Paolo II, Fisciano 84084, Italy

<sup>3</sup>Electronic Materials Research Laboratory, Xi'an Jiaotong University, Xi'an 710049, People's Republic of China <sup>4</sup>IHP Microelectronics, Im Technologie Park 25, 15236 Frankfurt (Oder), Germany

<sup>5</sup>Brandenburg University of Technology, Institute of Physics, Konrad Zuse Str. 1, 03046 Cottbus, Germany

2D MATERIALS 4 (2017) 025075

We propose a hybrid device consisting of a graphene/silicon (Gr/Si) Schottky diode in parallel with a Gr/SiO<sub>2</sub>/Si capacitor for high-performance photodetection. The device, fabricated by transfer of commercial graphene on low-doped n-type Si substrate, achieves a photoresponse as high as 3 AW<sup>-1</sup> and a normalized detectivity higher than  $3.5 \times 10^{12}$  cmHz<sup>1/2</sup> W<sup>-1</sup> in the visible range. It exhibits a photocurrent exceeding the forward current because photo-generated minority carriers, accumulated at Si/SiO<sub>2</sub> interface of the Gr/SiO<sub>2</sub>/Si capacitor, diffuse to the Gr/Si junction. We show that the same mechanism, when due to thermally generated carriers, although usually neglected or disregarded, causes the increased leakage often measured in Gr/Si heterojunctions. We perform extensive I–V and C-V characterization at different temperatures and we measure a zero-bias Schottky barrier height of 0.52 eV at room temperature, as well as an effective Richardson constant A<sup>\*\*</sup> = 4×10<sup>-5</sup> A cm<sup>-2</sup> K<sup>-2</sup> and an ideality factor n≈3.6, explained by a thin (<1 nm) oxide layer at the Gr/Si interface.

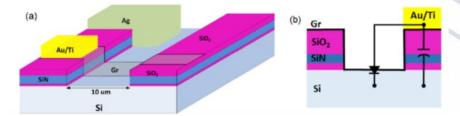

Fig.1: (a) 3D schematic view and (b) cross-section of Gr/Si diode in parallel with a Gr/SiO<sub>2</sub>–Si<sub>3</sub>N<sub>4</sub>–SiO<sub>2</sub>/Si MOS capacitor.

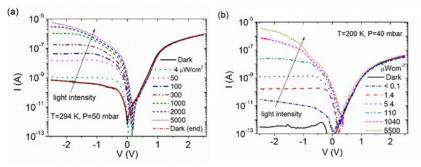

Fig.2: I-V characteristics of the Gr/Si junction for different illumination levels at T=294 K, P=50 mbar (a) and at T=200 K, P=40 mbar (b) after 5 days vacuum anneal.